联发科3纳米芯片2024年量产,集成电路设计赛道迎来新一轮竞速

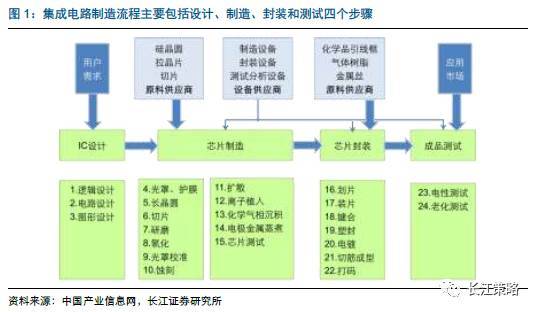

联发科正式确认其下一代旗舰移动平台将采用台积电3纳米制程工艺,并计划于2024年下半年投入量产。这一消息的公布,不仅标志着移动芯片制程工艺即将迈入全新阶段,更将全球半导体行业的目光聚焦于高端集成电路设计领域的激烈角逐,压力无疑已传导至其主要竞争对手——高通。

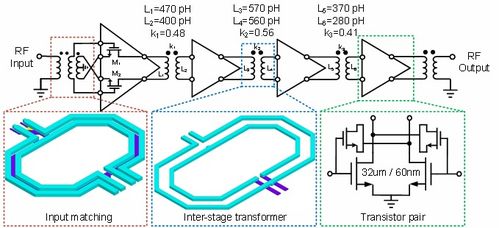

随着智能手机市场从增量竞争转向存量博弈,性能、能效与AI算力已成为决定旗舰产品体验的核心。联发科此番率先官宣3纳米量产时间表,意在抢占技术制高点,重塑其在高端市场的品牌形象与技术话语权。台积电的3纳米工艺相比现行的4纳米,预计将在晶体管密度提升约70%,在相同功耗下性能提升10%-15%,或在相同性能下功耗降低25%-30%。这为联发科设计更强大、更省电的SoC(系统级芯片)提供了坚实的物理基础,有望在能效比这一关键指标上实现显著突破。

压力由此给到了高通。作为移动芯片领域的长期领导者,高通近年来在旗舰平台上也面临着激烈的竞争与挑战。尽管其骁龙系列凭借强大的GPU性能和完整的生态合作体系保持着优势,但在制程工艺的率先采用上,联发科的激进路线构成了直接威胁。高通下一代旗舰芯片(预计为骁龙8 Gen 4)的制程选择与量产时间,将成为市场关注的焦点。业内普遍预计,高通很可能同样转向台积电的3纳米工艺(或部分采用),一场关于性能调校、能效优化与AI架构创新的“贴身肉搏”将在2024年全面展开。

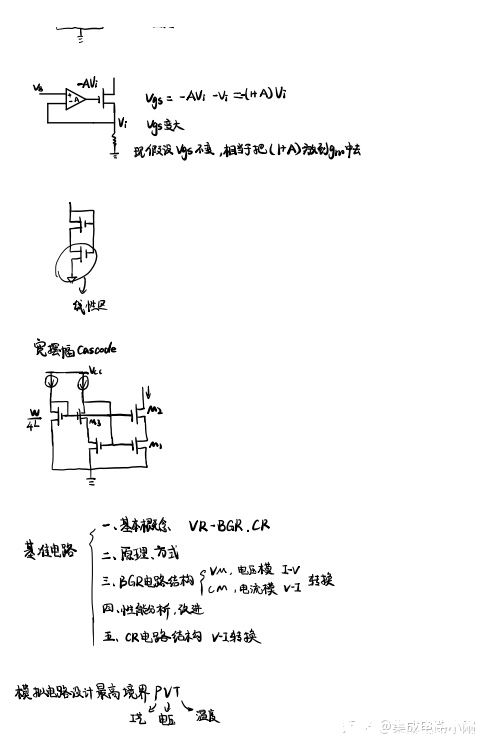

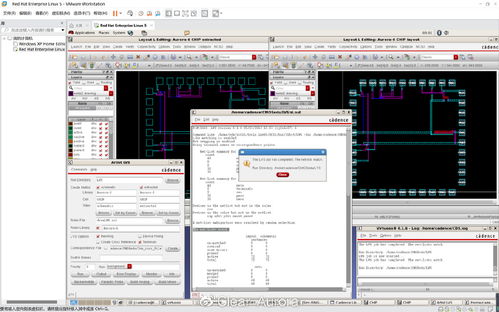

这场竞赛的深远影响,远不止于两家设计巨头的市场份额之争。它深刻揭示了全球集成电路设计行业的发展趋势:先进制程的军备竞赛已进入白热化阶段,设计公司必须与晶圆代工厂达成深度、排他性的战略合作,以获取稀缺的先进产能和工艺优化支持,技术壁垒与供应链门槛被进一步抬高。单纯追求制程数字的进步已不足以构成绝对优势,设计能力的重要性愈发凸显。如何在3纳米的物理基础上,通过创新的CPU/GPU/NPU架构、先进封装技术(如Chiplet)以及软硬件协同优化,挖掘出极致的性能与能效,才是真正的胜负手。随着手机市场增长趋缓,芯片的应用场景正加速向汽车、XR(扩展现实)、物联网、个人计算设备等多元化领域拓展。3纳米等高阶工艺所带来的算力与能效红利,将成为驱动这些下一代智能终端发展的核心引擎。

联发科的率先宣言,如同一块投入静湖的巨石,激起了层层涟漪。它预示着2024年将成为移动芯片乃至整个高端集成电路设计领域的一个关键年份。无论是联发科意图凭借工艺领先实现高端市场的进一步突破,还是高通如何捍卫其王座并予以回应,亦或是苹果A系列芯片的持续演进,都将共同推动着半导体技术的边界向前拓展。这场由最前沿制程工艺驱动的设计竞赛,其成果将转化为亿万消费者手中设备更强大的计算能力、更持久的续航体验和更智能的交互方式,持续塑造着我们的数字生活。

如若转载,请注明出处:http://www.kxkdqntm.com/product/79.html

更新时间:2026-04-08 06:43:38