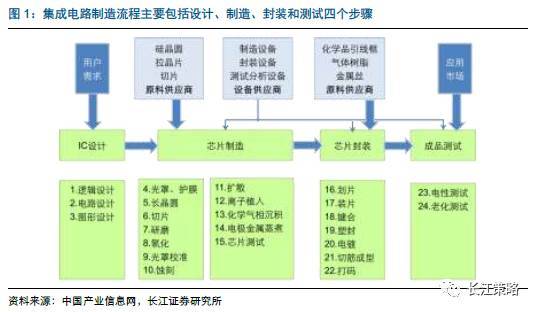

集成电路CAD设计中的关键环节 芯片焊盘与版图布局

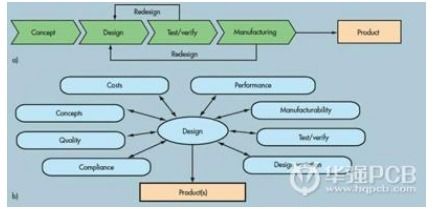

集成电路(IC)设计是一个高度复杂且精密的系统工程,其成功与否在很大程度上依赖于计算机辅助设计(CAD)工具的运用以及关键物理设计环节的把控。其中,芯片焊盘(Pad)设计与版图(Layout)布局设计是连接电路逻辑与物理实现的核心桥梁,直接决定了芯片的性能、可靠性及可制造性。

一、 芯片焊盘设计:芯片与外部世界的接口

芯片焊盘是集成电路芯片上用于与外部封装引脚或电路板进行电气连接和物理固定的金属区域。其设计绝非简单的金属块摆放,而需综合考虑多方面的因素:

- 电气特性:焊盘的尺寸、形状及其与内部电路的连接线(通常为上金属层)需要满足电流承载能力(电流密度)、阻抗匹配以及信号完整性的要求。例如,电源和地焊盘通常需要更大的面积以减小电阻和电感,而高频信号焊盘则需特别注意寄生参数的控制。

- 物理与可靠性:焊盘必须能够承受封装过程中的键合(Wire Bonding)或倒装焊(Flip-Chip)所带来的机械应力与热应力。设计时需要遵循设计规则(Design Rule),确保与相邻结构的间距,防止短路或长期可靠性问题(如电迁移)。

- 封装兼容性:焊盘的布局(排列顺序、间距)必须与选定的封装形式(如QFP、BGA、CSP等)的引脚框架或基板相匹配。合理的焊盘布局能简化封装布线,提升良率。

- 测试与调试:通常会设置专用的测试焊盘,用于生产过程中的芯片探针测试(CP Test),以验证晶圆级别的功能与性能。

在CAD设计流程中,焊盘通常作为一个特殊的库单元(Pad Cell)进行设计和调用,其设计需要与封装工程师密切协同。

二、 版图布局设计:电路功能的物理映射

版图布局是将经过逻辑综合和电路设计(原理图)验证后的电路,转化为一系列符合半导体制造工艺规则的几何图形(各层掩膜版图形)的过程。这是IC设计从“抽象”走向“实体”的关键一步。

版图设计的主要目标与挑战包括:

- 面积优化:在满足所有设计规则的前提下,尽可能减小芯片面积以降低制造成本。这需要对晶体管、标准单元、宏模块(如存储器、IP核)进行最紧凑的摆放(Floorplanning)。

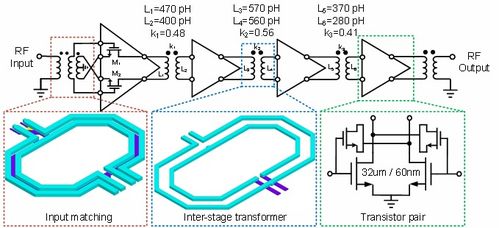

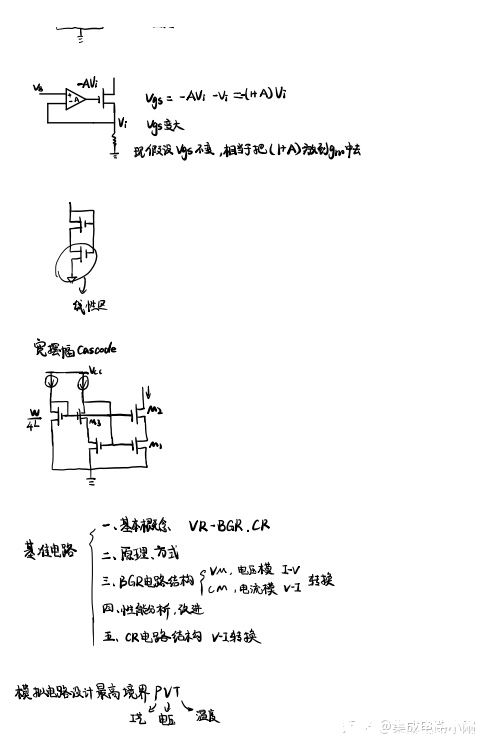

- 性能优化:布局布线直接影响信号的延迟、功耗和噪声。通过合理的布局,可以缩短关键路径(Critical Path)的连线长度,减少寄生电阻和电容,从而提升芯片速度。电源网络(Power Grid)的设计也至关重要,需确保整个芯片供电均匀稳定,压降(IR Drop)在允许范围内。

- 信号完整性:随着工艺节点进步,互连线间的串扰(Crosstalk)、时钟偏差(Skew)、电源地噪声等问题愈发突出。版图设计需要采用屏蔽、间距控制、插入缓冲器等手段来保障信号质量。

- 可制造性设计(DFM):现代版图设计必须考虑光刻工艺的局限性,主动采用添加冗余图形、进行光学邻近效应修正(OPC)等DFM技术,以提高实际制造中的图案保真度和良率。

- 可靠性设计(DFR):需考虑电迁移、热载流子注入、闩锁效应(Latch-up)等长期可靠性问题,并在版图中通过增加接触孔、添加保护环等结构进行预防。

三、 CAD工具在焊盘与版图设计中的核心作用

整个设计流程高度依赖于专业的IC CAD(或称EDA)工具链:

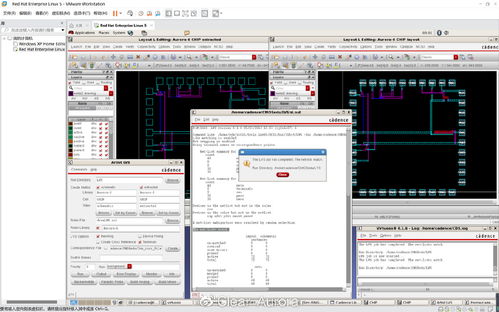

- 设计输入与规划:使用工具进行芯片的顶层规划,确定焊盘环(Pad Ring)的位置、核心功能区域(Core Area)的划分。

- 自动布局布线:对于数字电路,主要依靠自动布局布线工具,将数百万甚至数十亿个标准单元和宏模块在设定的约束下进行摆放和连线。工具会根据时序、功耗、拥塞度等目标进行迭代优化。

- 物理验证:这是确保设计成功的守门员。主要包括:

- 设计规则检查:验证版图是否符合代工厂的工艺规则。

- 电路图版图一致性检查:确保物理版图与原始电路图在电气连接上完全一致。

- 寄生参数提取与后仿真:从完成的版图中提取出详细的寄生电阻、电容、电感参数,并反标回电路进行仿真,以精确验证最终性能。

- 签核:在交付制造前,进行包括时序、功耗、信号完整性、电源完整性在内的全面签核分析,确保万无一失。

结论

芯片焊盘设计与版图布局设计是集成电路物理设计的两个紧密相连的支柱。焊盘是芯片对外沟通的“港口”,其设计关乎封装与测试的可行性;版图则是内部电路运行的“城市蓝图”,其优劣直接决定了芯片的效能、成本与可靠性。在先进工艺节点下,这两项工作的复杂性呈指数级增长,更加凸显了先进CAD/EDA工具与深厚设计经验相结合的重要性。成功的IC设计,必然是系统架构、电路设计、物理实现与制造工艺之间反复迭代、协同优化的结果,而焊盘与版图正是这一过程中承上启下的关键艺术与科学。

如若转载,请注明出处:http://www.kxkdqntm.com/product/71.html

更新时间:2026-04-14 13:15:05