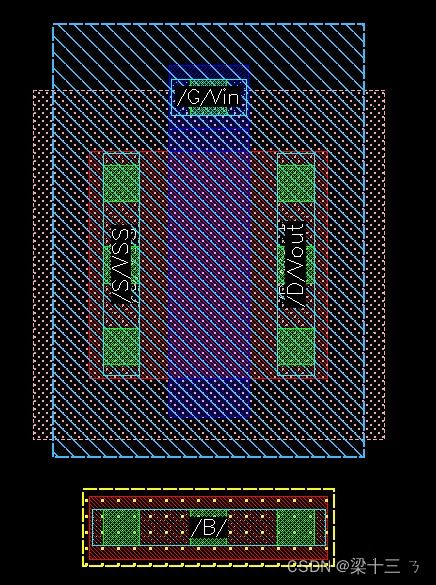

从0开始的Cadence Virtuoso模拟集成电路设计学习笔记(三) 反相器版图绘制与后仿真验证

在完成了反相器的电路设计与前仿真之后,我们正式进入模拟集成电路设计的核心物理实现环节——版图(Layout)设计,并对其进行后仿真验证。本笔记将详细记录在Cadence Virtuoso环境中,一个CMOS反相器从版图绘制到物理验证、提取寄生参数,最终完成后仿真的完整流程。

一、 版图设计:将电路图转化为物理图形

版图是电路的物理描述,是芯片制造的蓝图。在Virtuoso Layout Editor中,我们开始绘制反相器的版图。

- 创建与设置:在Library Manager中,为反相器电路图(schematic)创建对应的版图视图(Layout)。首先设置正确的工艺设计规则文件(Display.drf或TF文件),这决定了不同图层(如nwell, pplus, poly, metal1等)的颜色与填充样式。

- 核心器件绘制:

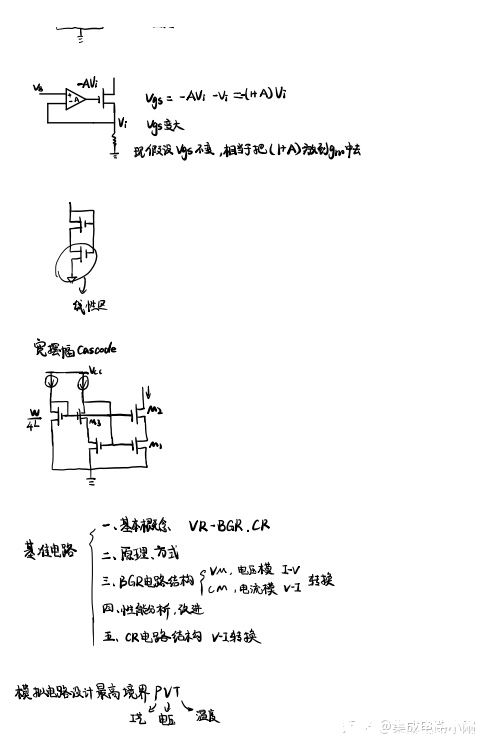

- PMOS与NMOS晶体管:使用

Instance工具调用PDK(工艺设计套件)中的标准MOS管版图单元,或根据W/L参数手动绘制。关键步骤包括:绘制有源区(Active),多晶硅栅(Poly),以及注入层(nplus/pplus)形成源漏区。PMOS管需要放置于N阱(Nwell)中。务必保证栅极对齐,这是反相器正常工作的基础。

- 连接:使用金属层(如Metal1)连接PMOS的漏极与NMOS的漏极作为输出端;连接PMOS的源极到VDD(电源,通常用高层金属如Metal2);连接NMOS的源极到VSS(地,用Metal1或Metal2)。输入端(栅极)也用Metal1连接至多晶硅。

- 遵循设计规则:绘制过程中,必须严格遵守DRC(设计规则检查)规则,包括最小线宽、最小间距、包围、延伸等。这是确保芯片可制造、良率高的生命线。

- 添加引脚与标签:使用

Pin工具创建输入(IN)、输出(OUT)、电源(VDD)和地(VSS)的物理引脚,并为其打上文本标签(Label),标签名称必须与电路图中的网络名一致,以便于后续的LVS比对。

二、 物理验证:确保版图正确无误

版图绘制完成后,必须通过严格的物理验证。

- DRC(设计规则检查):运行DRC,检查版图是否符合工艺厂的所有几何规则。Virtuoso通常集成Calibre或Assura等工具。必须解决所有DRC错误(Error)和警告(Warning),直至报告“clean”。

- LVS(版图与电路图一致性检查):这是至关重要的一步,用于验证绘制的版图是否与原始电路图在电气连接上完全一致。运行LVS工具,它会比较网表:

- 提取:从版图中提取出包含所有晶体管和连接的电路网表。

- 比对:将此网表与反相器电路图生成的网表进行比对。

- 成功标志是看到“NETS ARE EQUAL”和“DEVICES ARE EQUAL”的提示,表明版图与原理图匹配。

三、 寄生参数提取与后仿真

通过LVS后,版图在逻辑上已正确。但真实的版图存在寄生电阻(R)、寄生电容(C),甚至寄生电感(在高速设计中)。这些寄生效应会显著影响电路性能(如速度、功耗),因此必须进行后仿真(Post-layout Simulation)。

- 提取寄生参数:使用RCX(寄生参数提取)工具(如Quantus、Calibre xRC等)对通过验证的版图进行提取。工具会根据金属线的尺寸、间距、层间介质等信息,生成一个包含所有寄生R和C的详细网表(通常为SPICE格式)。

- 设置后仿真:

- 在Virtuoso ADE Explorer或ADE Assembler中,建立一个新的仿真环境。

- 在

Setup->Environment中,将Simulation标签下的Switch View List设置为包含extracted视图(即寄生参数提取后生成的视图),并确保其优先级高于schematic视图。这样仿真器就会调用包含寄生信息的网表进行仿真。

- 运行与结果分析:

- 施加与前仿真相同的测试条件(如输入脉冲信号、电源电压、负载电容等)。

- 运行瞬态分析(tran),观察输入输出波形。

- 关键对比:将后仿真结果与前仿真结果叠加对比。通常会观察到:

- 延迟增加:由于寄生RC的充放电,输出信号的上升/下降时间变长,传播延迟增加。

- 波形变缓:边沿不再像前仿真那样陡峭。

- 功耗可能微变:由于额外的寄生电容充放电,动态功耗可能略有上升。

四、 迭代与优化

如果后仿真性能(如延迟、功耗)不满足设计指标,则需要返回修改版图。常见的优化手段包括:

优化走线,缩短关键路径(如输出节点)的金属线长度以减少寄生电阻和电容。

使用更宽的金属线(在DRC允许范围内)以减少电阻。

* 重新规划器件布局,减少互连距离。

修改后,必须重新进行DRC、LVS和寄生参数提取,然后再次后仿真,直至性能达标。

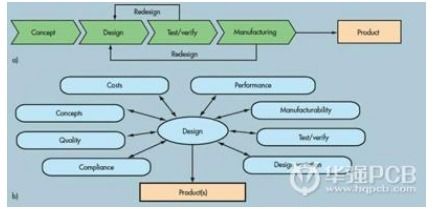

###

从电路图(Schematic)到版图(Layout),再到后仿真(Post-sim),是模拟IC设计从“理想”走向“现实”的必经之路。反相器作为最基本的单元,其流程清晰地展现了这一核心循环:设计 -> 物理实现 -> 验证(DRC/LVS)-> 评估性能(后仿真)-> 迭代优化。熟练掌握这一流程,是后续设计更复杂模拟电路(如放大器、比较器、PLL)的坚实基础。版图设计不仅要求电气正确,更是一门追求性能、面积与可靠性平衡的艺术。

如若转载,请注明出处:http://www.kxkdqntm.com/product/66.html

更新时间:2026-04-14 05:33:46