集成电路设计 现代电子科技的基石与创新引擎

在当今这个高度数字化的时代,集成电路(IC)已经渗透到我们生活的方方面面,从智能手机、个人电脑到智能家居、汽车电子,再到数据中心和人工智能系统,其无处不在的身影正悄然推动着社会的前进。而这一切的核心驱动力,正是集成电路设计这一高科技领域的持续创新与突破。

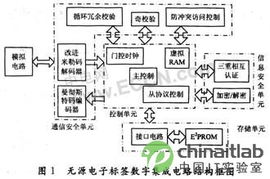

集成电路设计,简而言之,就是将数百万乃至数十亿个晶体管、电阻、电容等电子元件,通过精密的布局与连线,集成在一块微小的硅片上,以实现特定的复杂功能。它并非简单的物理堆叠,而是一个融合了物理学、材料科学、电子工程、计算机科学和数学等多学科知识的系统性创造过程。

设计流程:从概念到芯片的精密旅程

一个集成电路的诞生,通常始于一个明确的市场需求或一个创新的技术构想。整个设计流程可以概括为以下几个关键阶段:

- 系统架构与规格定义:明确芯片需要实现的功能、性能指标(如速度、功耗、面积)、工作环境以及成本目标。这是设计的“蓝图”阶段。

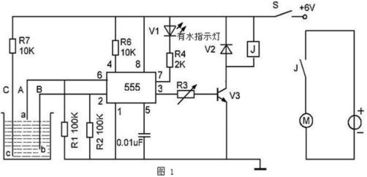

- 前端设计(逻辑设计):设计工程师使用硬件描述语言(如Verilog或VHDL)将架构转化为寄存器传输级(RTL)代码,描述电路的数字逻辑行为。随后进行功能仿真与验证,确保逻辑正确。

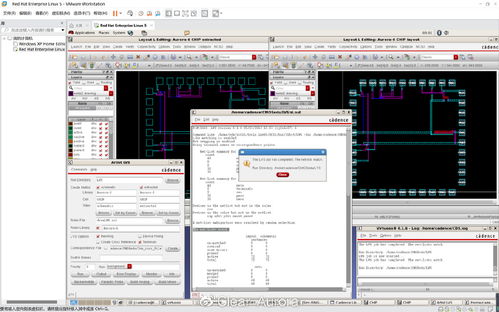

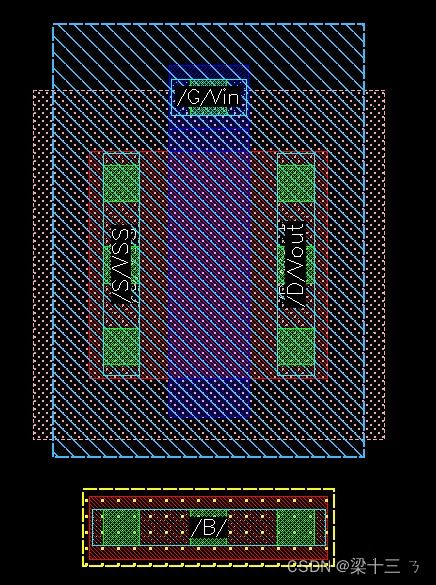

- 后端设计(物理设计):这是将RTL代码“翻译”成实际物理版图的过程。包括逻辑综合(将RTL转换为门级网表)、布局(确定每个元件在芯片上的位置)、布线(连接所有元件)、时序分析、功耗分析以及物理验证等。此阶段直接决定了芯片的最终性能、可靠性和制造成本。

- 制造与封测:将设计完成的版图数据(GDSII文件)交付给晶圆代工厂(Foundry)进行光刻、刻蚀、掺杂等工艺制造,形成晶圆。之后进行切割、封装成独立芯片,并进行严格的测试,确保良率与功能达标。

核心挑战与关键技术

随着工艺节点不断微缩至纳米级(如5nm、3nm甚至更小),集成电路设计面临着前所未有的挑战:

- 功耗与散热:晶体管密度飙升导致功耗密度激增,“功耗墙”问题日益突出。低功耗设计技术,如多阈值电压、电源门控、动态电压频率调整等,变得至关重要。

- 时序收敛与信号完整性:在高频下,互连线延迟、串扰、电源噪声等问题严重影响信号质量与时序。

- 设计与制造协同(DTCO):设计师必须深入理解先进工艺的物理限制(如光刻限制、器件变异),在设计中提前规避制造风险。

- 设计复杂度与成本:超大规模集成电路的设计周期长、投入巨大,需要高度自动化的电子设计自动化工具链支撑。

为了应对这些挑战,一系列创新设计方法和技术应运而生:

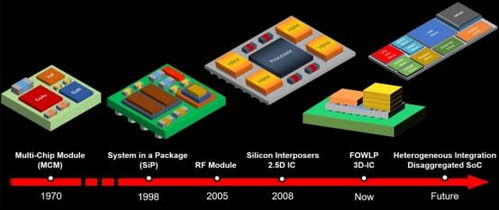

- 异构集成与Chiplet(芯粒)技术:不再追求将所有功能集成于单一巨型芯片,而是将不同工艺、不同功能的芯粒通过先进封装(如2.5D/3D IC)集成在一起,实现性能、成本与开发周期的优化。

- 基于AI/ML的设计自动化:利用机器学习优化布局布线、功耗预测、良率提升等,大幅提升设计效率与质量。

- 特定领域架构:针对人工智能、自动驾驶、高性能计算等特定应用,设计高度定制化的专用集成电路,在能效比上远超通用处理器。

未来展望

集成电路设计将继续沿着“更智能、更高效、更集成”的方向演进。随着新材料(如二维材料)、新器件(如环栅晶体管GAA)、新计算范式(如存算一体、量子计算)的探索,设计方法论也将发生深刻变革。开源硬件(如RISC-V指令集架构)的兴起,正降低设计门槛,推动产业生态的多元化与创新活力。

总而言之,集成电路设计是连接创新思想与物理实现的桥梁,是信息产业皇冠上的明珠。它不仅是一门精密的工程技术,更是一门充满艺术性的创造学问。对于有志于投身这一领域的工程师和研究者而言,它意味着无限的挑战与机遇,是塑造未来智能世界的核心力量。

如若转载,请注明出处:http://www.kxkdqntm.com/product/58.html

更新时间:2026-04-14 00:23:29