集成电路CAD设计中的关键环节 芯片焊盘与版图布局设计探析

集成电路(IC)设计是一个高度复杂且精密的系统工程,而计算机辅助设计(CAD)工具的应用极大地推动了其发展。在IC设计的后端物理实现阶段,芯片焊盘(Pad)设计与版图(Layout)布局设计是两个至关重要且紧密相连的环节,直接决定了芯片的性能、可靠性、可制造性及最终成本。

一、 芯片焊盘设计:芯片与外部世界的桥梁

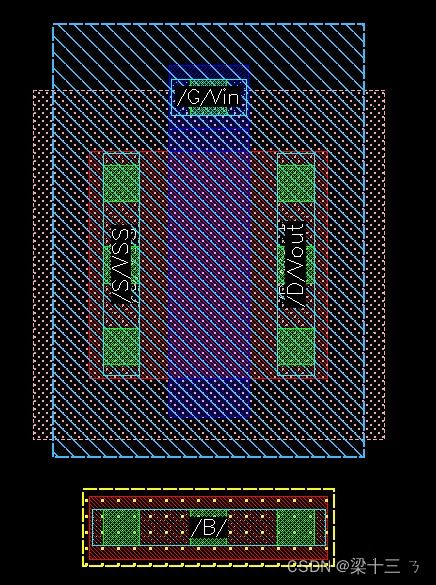

芯片焊盘是集成电路裸片(Die)上用于与外部封装引脚或基板进行电气连接和机械固定的金属化区域。其设计绝非简单的几何图形绘制,而需综合考量电学、热学、机械及工艺等多方面因素。

核心设计要点包括:

1. 电气特性: 焊盘的大小、形状及其与内部电路的连接线(通常通过顶层金属实现)会影响信号完整性,尤其是高频信号。需要考虑阻抗匹配、减小寄生电感与电容,以及防止信号串扰。对于电源和地焊盘,往往需要设计得更大或使用多个焊盘并联,以降低电阻和电感,确保稳定的供电。

2. 可靠性: 焊盘需要承受封装过程中的键合(如金丝球焊、楔形焊)或倒装焊(Flip-Chip)带来的机械应力和热应力。设计需满足一定的尺寸规则,确保键合强度,并考虑压点区域(Bonding Area)与芯片内部有源器件的安全距离(Keep-Out Area),防止应力损伤。

3. 布局规划: 焊盘通常沿芯片周边排列(Perimeter Pad)或在芯片表面阵列分布(Area Array Pad,如Flip-Chip)。其位置规划需与封装类型(如QFP、BGA、CSP等)的引脚排布相匹配,同时优化内部走线,避免绕线过长。I/O焊盘环(I/O Pad Ring)的设计是芯片与核心逻辑区域的缓冲与接口。

4. ESD保护: 每一个对外连接的焊盘都必须集成静电放电(ESD)保护电路,以防止芯片在制造、测试、运输和使用过程中被静电击穿。ESD保护结构的设计与焊盘布局需协同进行。

二、 版图布局设计:性能与工艺的物理蓝图

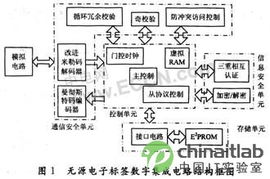

版图布局设计是将电路逻辑网表(Netlist)转化为一系列符合制造工艺规则的几何图形(各层掩模图形)的过程。它是电路设计思想的物理实现,是性能、面积、功耗等指标博弈的战场。

核心设计原则与流程包括:

1. 规划与分区: 根据电路功能模块(如模拟模块、数字逻辑、存储器、电源管理等)进行芯片面积的初步规划与分区。合理的布局可以缩短关键路径连线,减少信号延迟和互连寄生效应,同时有利于电源网络的均匀分布。

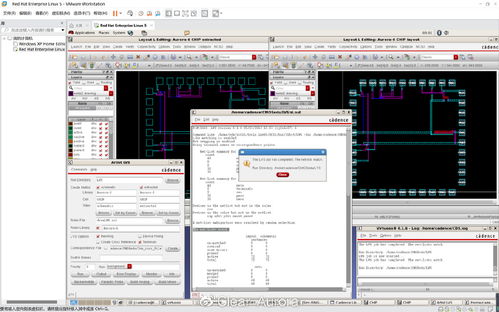

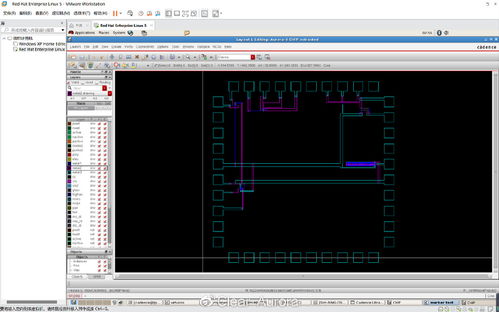

2. 单元布局与布线: 使用CAD工具进行标准单元或定制单元的自动布局(Placement)和布线(Routing)。布局追求连线总长最短、时序收敛;布线则需在有限的互连层资源中完成所有逻辑连接,并满足设计规则检查(DRC)和电气规则检查(ERC)。

3. 时钟树综合: 为整个芯片构建低偏移(Skew)、低延迟的时钟分布网络,是高性能数字芯片布局中的核心任务。时钟树的拓扑结构和物理布局直接影响芯片的最高工作频率。

4. 电源/地网络设计: 设计 robust 的电源(VDD)和地(VSS)网格,为所有电路模块提供稳定、低噪声的供电。这涉及电源环(Power Ring)、电源条带(Power Stripe)以及大量通孔(Via)的设计,需考虑电流密度和电压降(IR Drop)。

5. 设计验证: 布局完成后,必须进行一系列严格的验证,包括DRC(确保图形符合工艺制造极限)、LVS(版图与电路图一致性检查)、寄生参数提取(RC Extraction)以及基于带寄生参数的时序分析(Post-Layout Simulation)和信号完整性分析(如串扰、电迁移)。

三、 焊盘设计与版图布局的协同

焊盘设计与整体版图布局并非孤立进行,而是需要深度协同:

- 接口与规划: I/O焊盘环的布局是芯片版图规划的第一步,它框定了核心区域(Core Area)的范围。焊盘的位置决定了I/O信号进入芯片的入口点,进而影响内部模块的布局和全局布线的走向。

- 电源完整性: 电源和地焊盘的数量、位置以及它们与内部电源网格的连接方式,共同决定了电源配送网络的阻抗和噪声水平。

- 封装协同设计: 现代高性能芯片往往需要与封装进行协同设计(Co-Design)。焊盘的布局(尤其是Flip-Chip的凸点布局)必须与封装基板的布线能力、热膨胀系数匹配以及散热路径规划相结合。

###

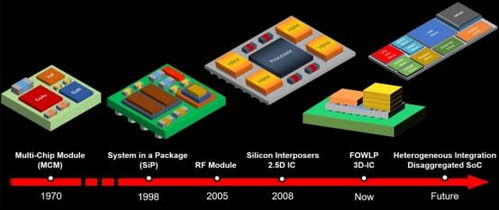

集成电路CAD设计中的芯片焊盘与版图布局设计,是将抽象电路转化为可制造硅片的关键桥梁。它们深度融合了电路知识、物理理解、工艺技术和工程经验。随着工艺节点不断演进至纳米尺度,以及系统级封装(SiP)、芯粒(Chiplet)等新技术的兴起,这两项设计工作面临的挑战日益严峻,其重要性也愈加凸显。优秀的焊盘与版图设计,是保证芯片一次流片成功、达成预期性能指标的坚实基石。

如若转载,请注明出处:http://www.kxkdqntm.com/product/49.html

更新时间:2026-04-14 21:14:26