三维视角下的集成电路设计新思路 超越平面的创新蓝图

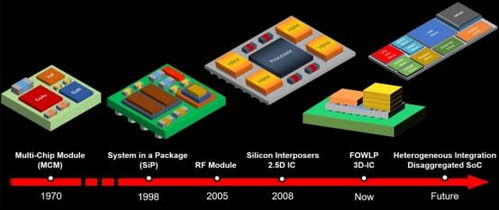

随着摩尔定律逐渐逼近物理极限,传统二维平面集成电路设计正面临前所未有的挑战。为了延续计算能力的指数级增长,并满足人工智能、物联网、高性能计算等新兴应用对更高密度、更低功耗、更强性能的迫切需求,集成电路设计必须寻求范式突破。将设计视角从二维平面拓展到三维空间,正成为引领下一代芯片发展的关键新思路。

一、 三维集成:从堆叠到异构

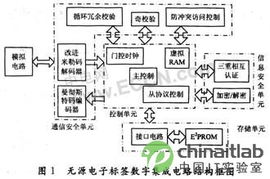

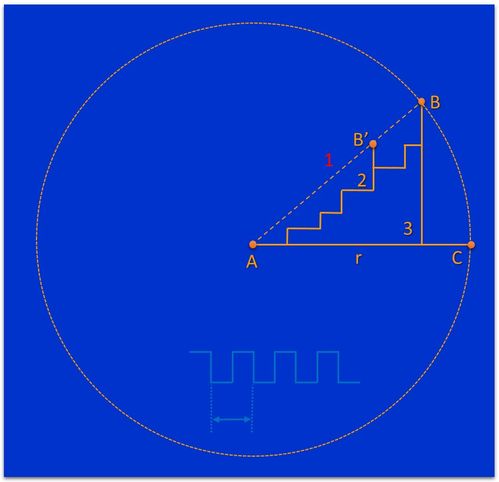

三维集成电路设计的核心在于,通过垂直方向(Z轴)的拓展,将多个功能层(如计算单元、存储单元、光电模块等)以先进封装或直接键合技术集成在一起。这不仅仅是简单的物理堆叠,更是一种系统级的协同设计思路。例如,通过将高带宽内存(HBM)与处理器核心进行3D堆叠,可以极大缩短互连距离,实现远超传统二维封装的数据传输速率和能效比,有效缓解“内存墙”问题。更进一步,三维异构集成允许将基于不同工艺节点、不同材料(如硅、三五族化合物)甚至不同功能原理(如数字、模拟、射频、MEMS、光子)的芯片或芯粒(Chiplet)垂直集成,形成功能更强大、更灵活的“超级芯片”系统。

二、 设计范式的三维重构

从设计方法论角度看,三维视角要求设计师彻底重构设计流程与工具。

- 系统架构层面:设计重心从单一芯片的平面布局规划,转向多芯片/多层的立体架构探索。需要综合考虑热管理(热量在垂直方向的积累与散发)、供电网络(三维供电)、信号完整性(穿过硅通孔TSV或混合键合界面的信号传输)以及测试策略等前所未有的三维耦合问题。

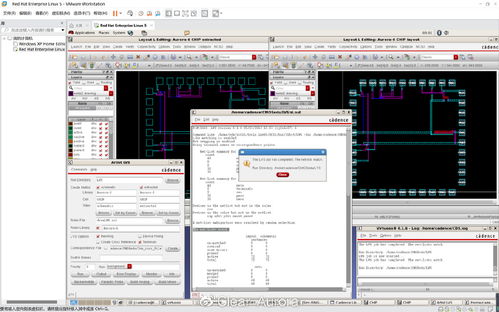

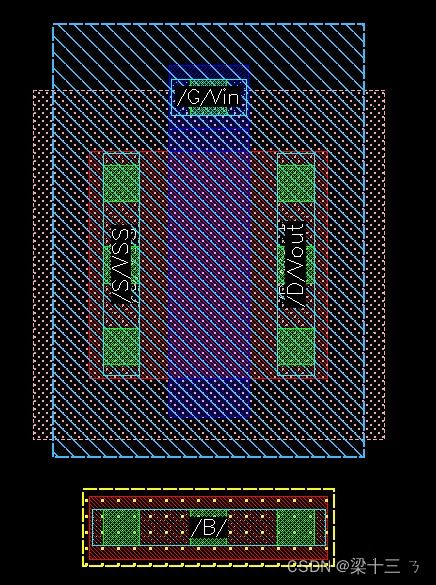

- 物理设计与EDA工具:传统的二维布局布线工具必须升级,以支持在多层之间进行器件摆放、逻辑单元划分和互连优化。热仿真、应力分析和3D寄生参数提取工具变得至关重要。这推动了电子设计自动化(EDA)向涵盖芯片、中介层、封装乃至系统的“3D-IC Co-Design”协同设计平台演进。

- 设计-制造协同:三维设计模糊了芯片设计与封装的界限,要求设计与制造环节更紧密地协作。设计规则必须充分考虑键合、TSV制造、微凸点等三维工艺的约束和可能性,实现“设计即制造”的深度融合。

三、 新思路带来的机遇与挑战

三维设计思路开辟了广阔的新机遇:

- 性能飞跃:缩短互连、增加带宽、降低功耗。

- 功能多样化:实现真正意义上的片上系统(SoC)与片上系统(SiP)融合。

- 灵活性与成本优化:通过芯粒复用,像搭积木一样组合不同IP,降低复杂芯片的开发成本和风险,加速产品上市。

挑战也同样严峻:

- 热管理难题:垂直堆叠导致功率密度剧增,散热成为首要瓶颈,需要创新性的冷却方案(如微流体冷却、热电冷却等)。

- 设计复杂性爆炸:多物理场耦合分析、测试与诊断、可靠性保障的难度呈指数增长。

- 产业链与生态重塑:需要建立新的IP复用标准、接口协议、测试标准以及商业模式。

三维视角的集成电路设计不仅是技术路径的延伸,更是思维方式的革新。它将推动芯片从“计算单元”向“集成智能系统”演进。随着材料科学、制造工艺和EDA工具的持续突破,结合人工智能驱动的设计自动化,三维集成电路设计必将解锁新的性能维度,为万物智能的时代构筑更强大的数字基石。从平面到立体的这一跃迁,正在重新绘制全球半导体产业竞争的版图。

如若转载,请注明出处:http://www.kxkdqntm.com/product/48.html

更新时间:2026-04-14 16:12:03